Personnaliséierten Hard Gold PCB Board FR4 steiwe Multilayer PCB Fabrikatioun

Basis Info

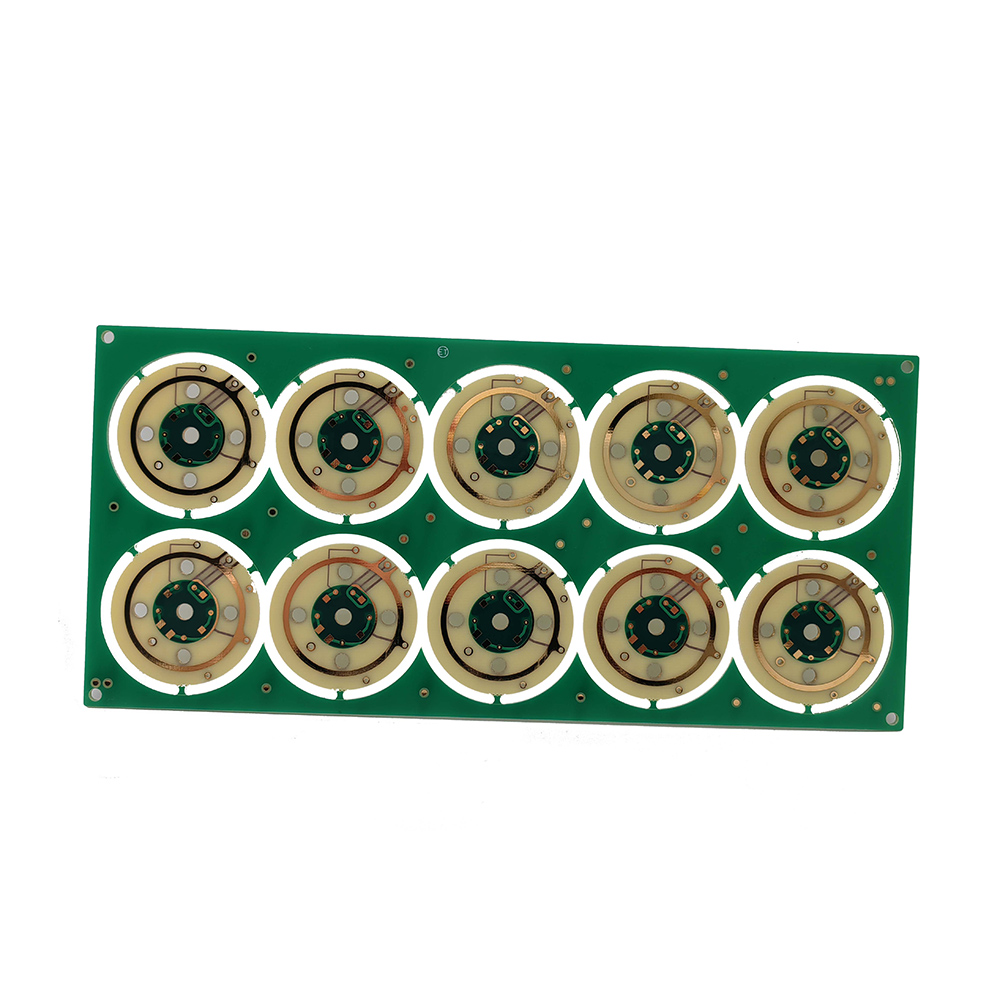

| Modell Nr. | PCB-A14 Fotoen |

| Transport Package | Vakuum Verpakung |

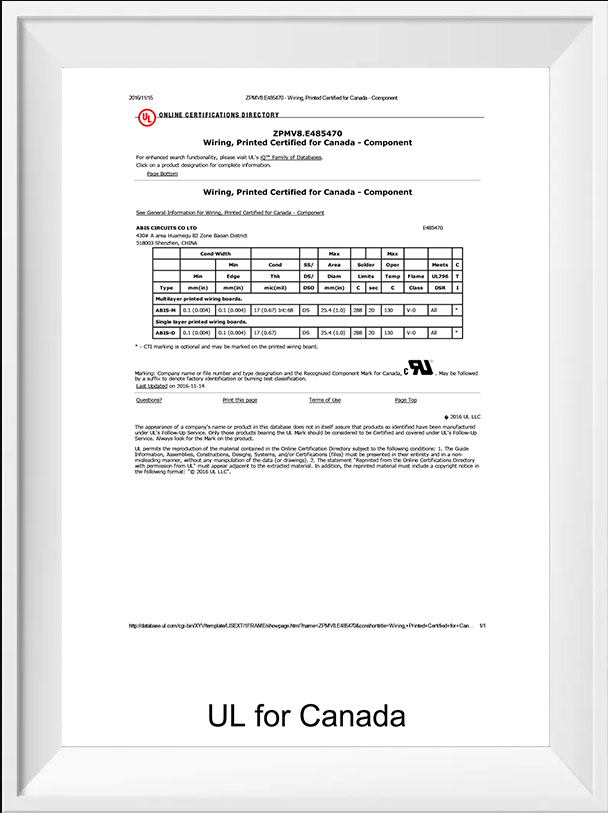

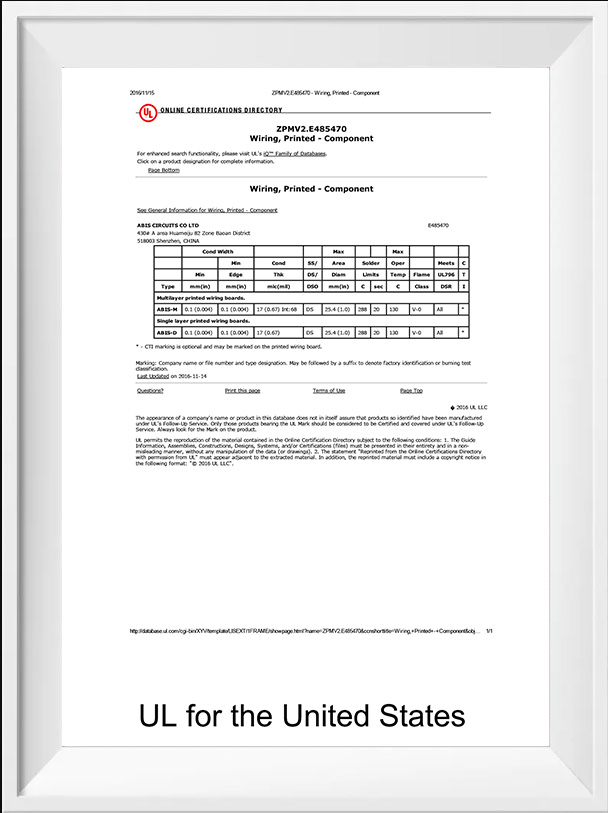

| Zertifikatioun | UL, ISO9001 & ISO14001, RoHS |

| Applikatioun | Konsument elektronesch |

| Minimum Plaz / Linn | 0,075 mm/3 mil |

| Produktioun Kapazitéit | 50.000 sqm / Mount |

| HS Code | 853400900 |

| Urspronk | A China hiergestallt |

Produkt beschreiwung

FR4 PCB Aféierung

FR heescht "Flam-retardant", FR-4 (oder FR4) ass eng NEMA-Grad Bezeechnung fir Glas-verstäerkt Epoxy Laminatmaterial, e Kompositmaterial aus gewéckelt Glasfaser Stoff mat engem Epoxyharzbinder, deen et en ideale Substrat fir elektronesch Komponenten mécht op engem gedréckte Circuit Verwaltungsrot.

Virdeeler an Nodeeler vun FR4 PCB

FR-4 Material ass sou populär wéinst senge ville wonnerbare Qualitéiten déi gedréckte Circuitboards profitéiere kënnen.Zousätzlech zu bezuelbar an einfach ze schaffen, ass et en elektreschen Isolator mat ganz héijer dielektrescher Kraaft.Plus, et ass haltbar, Feuchtigkeitbeständeg, Temperaturbeständeg a liicht.

FR-4 ass e wäit relevant Material, populär meeschtens fir seng niddreg Käschten a relativ mechanesch an elektresch Stabilitéit.Och wann dëst Material extensiv Virdeeler huet an a verschiddene Dicken a Gréissten verfügbar ass, ass et net déi bescht Wiel fir all Applikatioun, besonnesch Héichfrequenz Uwendungen wéi RF a Mikrowellendesignen.

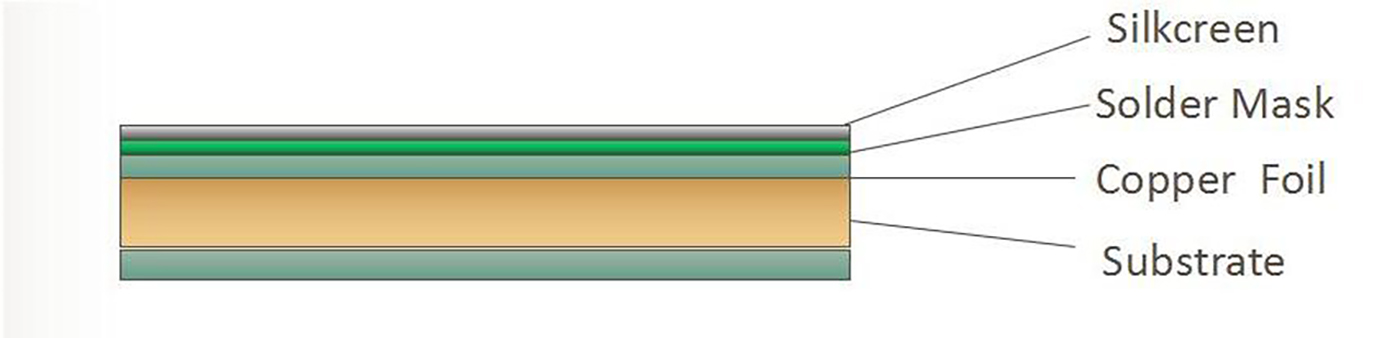

Duebel Säit PCBs Struktur

Duebelsäiteg PCBs si méiglecherweis déi allgemengst Aart vu PCBs.Am Géigesaz zu Single Layer PCBs, déi konduktiv Schicht op enger Säit vum Board hunn, kënnt de Double Sided PCB mat konduktiver Kupferschicht op béide Säiten vum Board.Elektronesch Kreesleef op enger Säit vun der Verwaltungsrot kann op der anerer Säit vun der Verwaltungsrot mat der Hëllef vun Lächer verbonne ginn (vias) duerch de Verwaltungsrot gebuert.D'Kapazitéit fir Weeër vun uewe bis ënnen ze kräizen erhöht d'Flexibilitéit vum Circuitdesigner beim Design vun de Circuiten staark a léint sech op eng staark erhéicht Circuitdicht.

Multi-Layer PCB Struktur

Multilayer PCBs erhéicht d'Komplexitéit an d'Dicht vun de PCB-Designen weider andeems zousätzlech Schichten iwwer déi iewescht an ënnen Schichten bäigefüügt ginn, déi an doppelseiteg Brieder gesi ginn.Multilayer PCBs ginn gebaut andeems déi verschidde Schichten laminéiert ginn.Déi bannescht Schichten, normalerweis doppelseiteg Circuitboards, sinn zesummegestapelt, mat Isoléierschichten tëscht an tëscht der Kupferfolie fir déi äusser Schichten.Lächer, déi duerch d'Brett gebohrt sinn (vias) wäerte Verbindunge mat de verschiddene Schichten vum Brett maachen.

Wou kënnt d'Harzmaterial bei ABIS hier?

Déi meescht vun hinnen aus Shengyi Technology Co., Ltd. (Modell S1000-2, S1141, S1165, S1600) ginn haaptsächlech benotzt fir eenzel an zweesäiteg gedréckte Circuitboards wéi och Multi-Layer Boards ze maachen.Hei kënnt Detailer fir Är Referenz.

Fir FR-4: Sheng Yi, King Board, Nan Ya, Polycard, ITEQ, ISOLA

Fir CEM-1 & CEM 3: Sheng Yi, King Board

Fir Héichfrequenz: Sheng Yi

Fir UV Cure: Tamura, Chang Xing (* Verfügbar Faarf: Gréng) Solder fir Single Side

Fir Liquid Photo: Tao Yang, Resist (Wet Film)

Chuan Yu (* Verfügbar Faarwen: Wäiss, Imaginable Solder Yellow, Purple, Red, Blue, Green, Black)

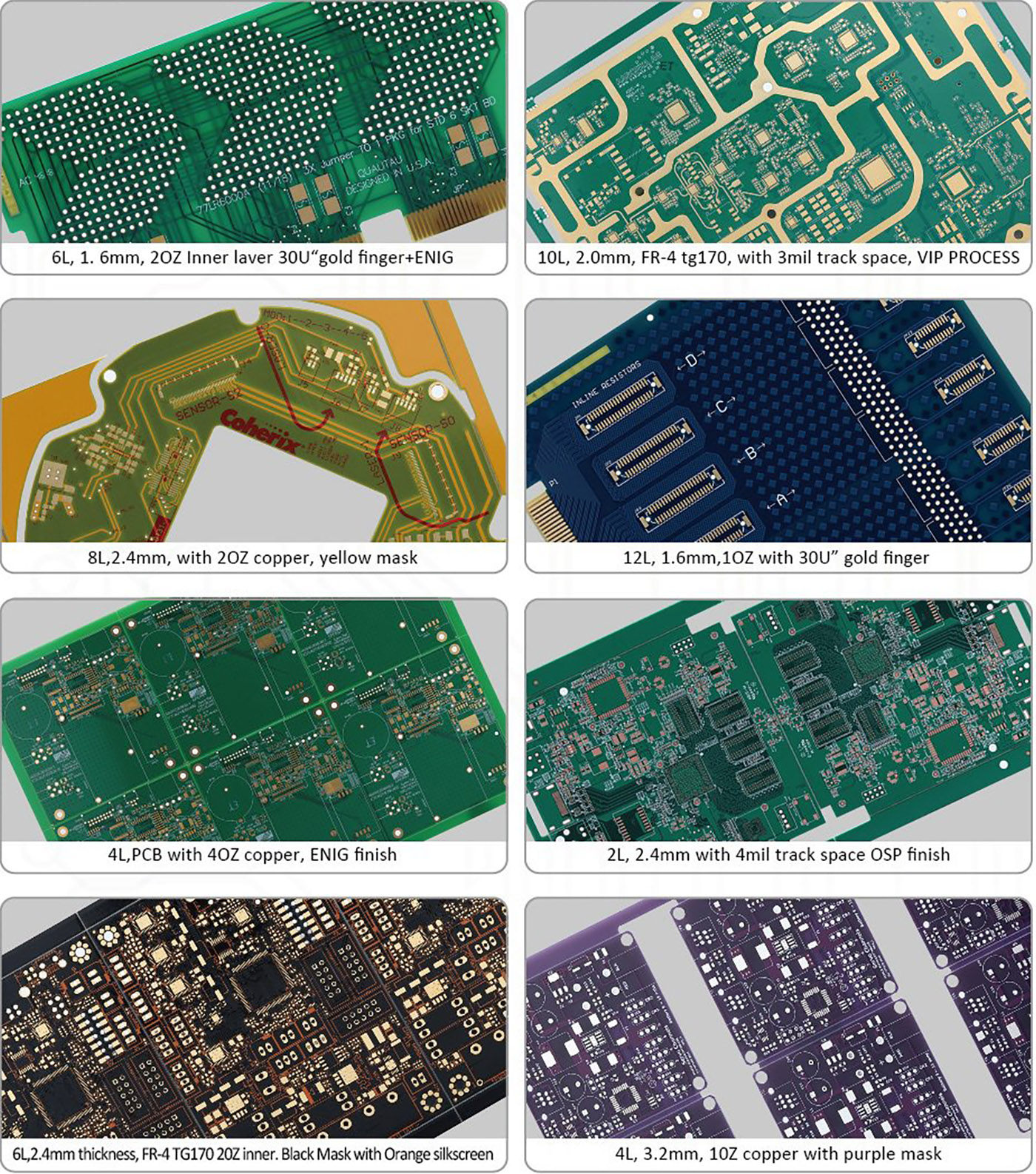

Technesch & Kapazitéit

ABIS erfuerene fir speziell Materialien fir steif PCB ze maachen, wéi: CEM-1 / CEM-3, PI, High Tg, Rogers, PTEF, Alu / Cu Base, etc. Drënner ass e kuerzen Iwwerbléck FYI.

| Artikel | Produktioun Kapazitéit |

| Layer zielt | 1-20 Schichten |

| Material | FR-4, CEM-1/CEM-3, PI, High Tg, Rogers, PTEF, Alu/Cu Base, etc. |

| Verwaltungsrot deck | 0,10 mm-8,00 mm |

| Maximal Gréisst | 600 mm x 1200 mm |

| Bord Outline Toleranz | +0,10 mm |

| Dicke Toleranz (t≥0.8mm) | ± 8% |

| Dicke Toleranz (t<0,8 mm) | ± 10% |

| Isolatioun Layer Dicke | 0,075 mm - 5,00 mm |

| Minimum Linn | 0,075 mm |

| Minimum Plaz | 0,075 mm |

| Eraus Layer Kupfer Dicke | 18-350 Uhr |

| Innere Layer Kupferdicke | 17 - 175 Uhr Do |

| Drilling Hole (mechanesch) | 0,15 mm - 6,35 mm |

| Finish Hole (mechanesch) | 0,10-6,30 mm |

| Duerchmiesser Toleranz (mechanesch) | 0,05 mm ép |

| Aschreiwung (mechanesch) | 0,075 mm |

| Aspekt Verhältnis | 16:1 |

| Solder Mask Typ | LPI |

| SMT Mini.Solder Mask Breet | 0,075 mm |

| Mini.Solder Mask Clearance | 0,05 mm ép |

| Plug Lach Duerchmiesser | 0,25 mm - 0,60 mm |

| Impedanz Kontroll Toleranz | ± 10% |

| Surface Finish / Behandlung | HASL, ENIG, Chem, Zinn, Flash Gold, OSP, Gold Finger |

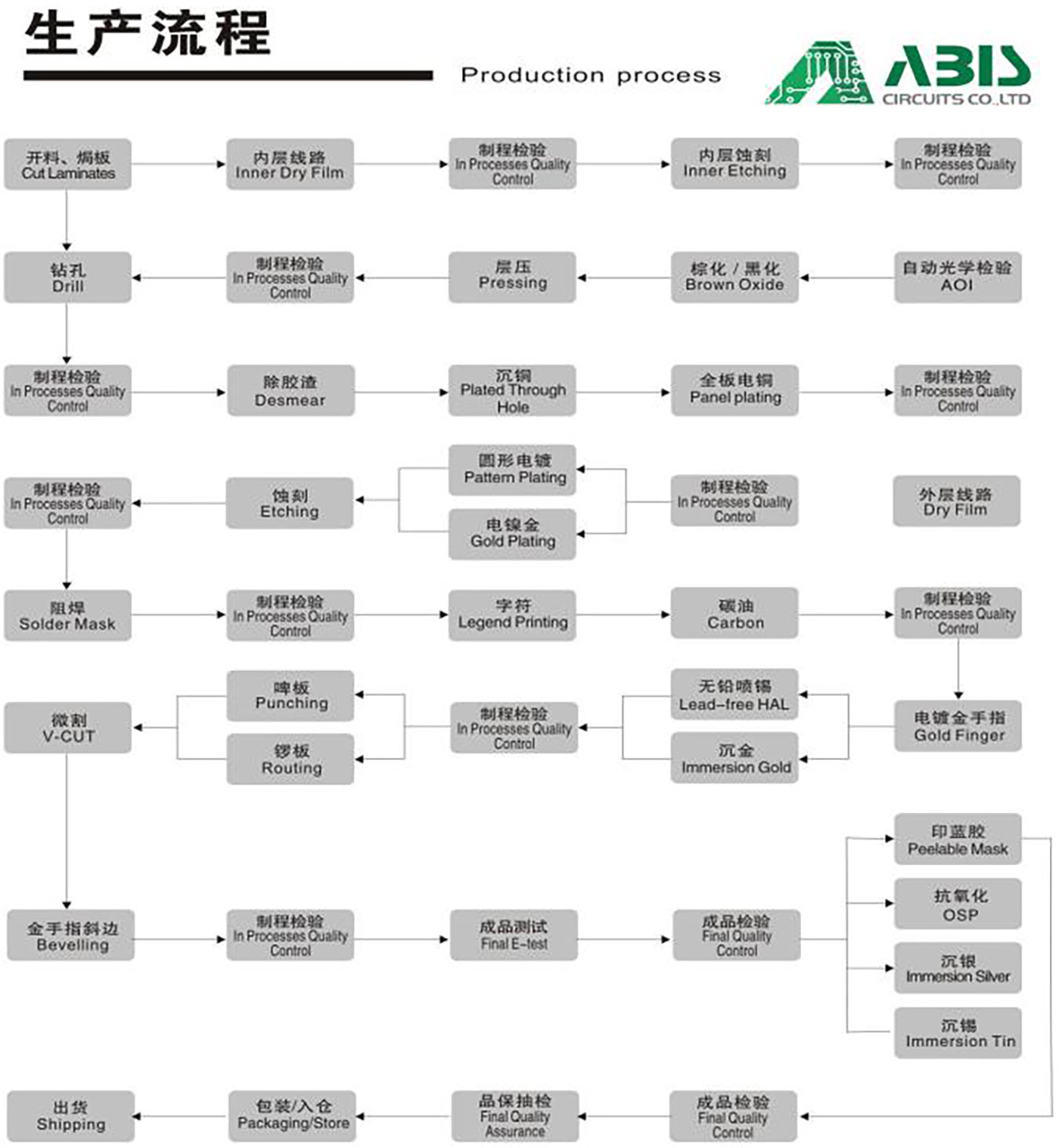

PCB Produktioun Prozess

De Prozess fänkt un mam Design vun der Layout vum PCB mat all PCB Design Software / CAD Tool (Proteus, Eagle, Oder CAD).

All Rescht vun de Schrëtt si vum Fabrikatiounsprozess vun engem steife Printed Circuit Board ass d'selwecht wéi Single Sided PCB oder Double Sided PCB oder Multi-Layer PCB.

Q / T Lead Time

| Kategorie | Schnellsten Lead Time | Normal Lead Time |

| Duebelsäiteg | 24h00 | 120 Uhr |

| 4 Schichten | 48h00 | 172 Uhr |

| 6 Schichten | 72h00 | 192 Uhr |

| 8 Schichten | 9 6h | 212 Uhr |

| 10 Schichten | 120 Uhr | 2 68h |

| 12 Schichten | 120 Uhr | 2 80h |

| 14 Schichten | 144 Uhr | 2 92h |

| 16-20 Schichten | Hänkt op déi spezifesch Ufuerderungen of | |

| Iwwer 20 Schichten | Hänkt op déi spezifesch Ufuerderungen of | |

ABIS 'Beweegung fir FR4 PCBS ze kontrolléieren

Lach Virbereedung

Dreck suergfälteg ewechhuelen & Buermaschinn Parameteren upassen: ier Dir mat Kupfer platéiert, bezilt ABIS héich Opmierksamkeet op all Lächer op engem FR4 PCB behandelt fir Schutt, Uewerfläch Onregelméissegkeeten an Epoxyschmier ze entfernen, déi propper Lächer suergen datt d'Platéierung erfollegräich un d'Lachmauer hält .och, fréi am Prozess, Buermaschinn Parameteren präziist ugepasst.

Uewerfläch Virbereedung

Deburring virsiichteg: eis erfuerene Tech Aarbechter wäerte sech virdru bewosst sinn datt deen eenzege Wee fir e schlecht Resultat ze vermeiden ass de Besoin fir speziell Handhabung virauszegesinn an déi entspriechend Schrëtt ze huelen fir sécher ze sinn datt de Prozess suergfälteg a korrekt gemaach gëtt.

Thermal Expansioun Tariffer

Gewunnecht mat de verschiddene Materialien ze handelen, wäert ABIS d'Kombinatioun analyséieren fir sécher ze sinn datt se passend ass.dann halen déi laangfristeg Zouverlässegkeet vun der CTE (koeffizient vun thermesch Expansioun), mat der ënneschten CTE, der manner wahrscheinlech déi plated duerch Lächer sinn aus widderholl flexing vun der Koffer ze versoen déi intern Schicht interconnections Formen.

Skaléieren

ABIS kontrolléiert d'Schaltung gëtt duerch bekannte Prozentzuelen an Erwaardung vun dësem Verloscht opskaléiert, sou datt d'Schichten op hir entworf Dimensiounen zréckkommen nodeems de Laminéierungszyklus fäerdeg ass.och, benotzt de Laminat Hiersteller d'Basis Skaléierungsempfehlungen a Kombinatioun mat internen statistesche Prozesskontrolldaten, fir Skalafaktoren ze wielen, déi mat der Zäit an deem bestëmmte Fabrikatiounsëmfeld konsequent sinn.

Machining

Wann d'Zäit kënnt fir Äre PCB ze bauen, sidd ABIS sécher datt Dir déi richteg Ausrüstung an d'Erfahrung hutt fir se am éischte Versuch richteg ze produzéieren.

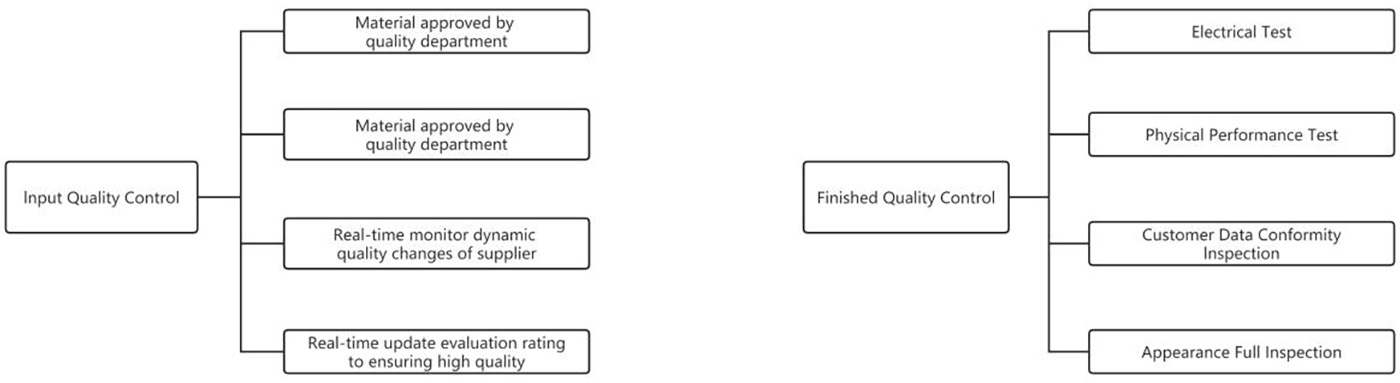

Qualitéitskontroll

BIS léist den Aluminium PCB Problem?

Matière première gi strikt kontrolléiert:De Passrate vun erakommen Material iwwer 99,9%.D'Zuel vun de Mass Oflehnungsraten ass ënner 0,01%.

Kupfer Ätz kontrolléiert:d'Kupferfolie, déi an Aluminium PCBs benotzt gëtt, ass vergläichbar méi déck.Wann d'Kupferfolie awer iwwer 3oz ass, erfuerdert d'Ätzen Breetkompensatioun.Mat der héich Präzisioun Ausrüstung aus Däitschland importéiert, erreecht d'min Breet / Raum mir kontrolléieren kann 0.01mm.D'Spurebreetkompensatioun gëtt präzis entworf fir d'Spurebreet aus Toleranz no Ätzen ze vermeiden.

Héich Qualitéit Solder Mask Dréckerei:Wéi mir all wëssen, ass et Schwieregkeeten am solder Mask Dréckerei vun Al PCB wéinst Koffer décke.Dëst ass well wann d'Spure Kupfer ze déck ass, da wäert d'Bild geätzt e groussen Ënnerscheed tëscht Spueroberfläche a Basisplat hunn an d'Lötmaske Dréckerei wäert schwéier sinn.Mir insistéieren op déi héchste Standarden vun solder Mask Ueleg am ganze Prozess, vun der eent bis déi zwee-Zäit solder Mask Dréckerei.

Mechanesch Fabrikatioun:Fir d'elektresch Kraaft ze vermeiden, déi duerch de mechanesche Fabrikatiounsprozess verursaacht gëtt, beinhalt mechanesch Bueraarbechten, Formen a V-Scoring etc. Dofir, fir niddereg-Volumen-Fabrikatioun vu Produkter, prioritär mir d'elektresch Milling a berufflech Milling Cutter ze benotzen.Och bezuele mir héich Opmierksamkeet fir d'Buerparameter unzepassen an d'Burr ze vermeiden.

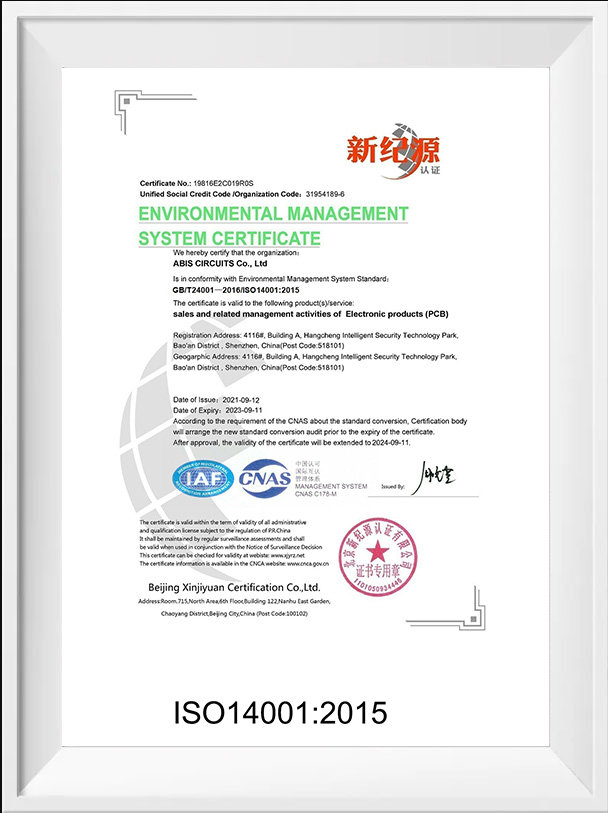

Zertifikat

FAQ

Iwwerpréift bannent 12 Stonnen.Wann d'Fro vum Ingenieur an d'Aarbechtsdatei gepréift ass, fänken mir d'Produktioun un.

ISO9001, ISO14001, UL USA & USA Kanada, IFA16949, SGS, RoHS Bericht.

Eis Qualitéitssécherungsprozeduren wéi hei ënnen:

a), Visuell Inspektioun

b), Fléien Sonde, Fixture Tool

c) Impedanzkontrolle

d), Solderfäegkeet Detektioun

e), Digital Metallo-Graghic Mikroskop

f), AOI (Automatiséiert Optesch Inspektioun)

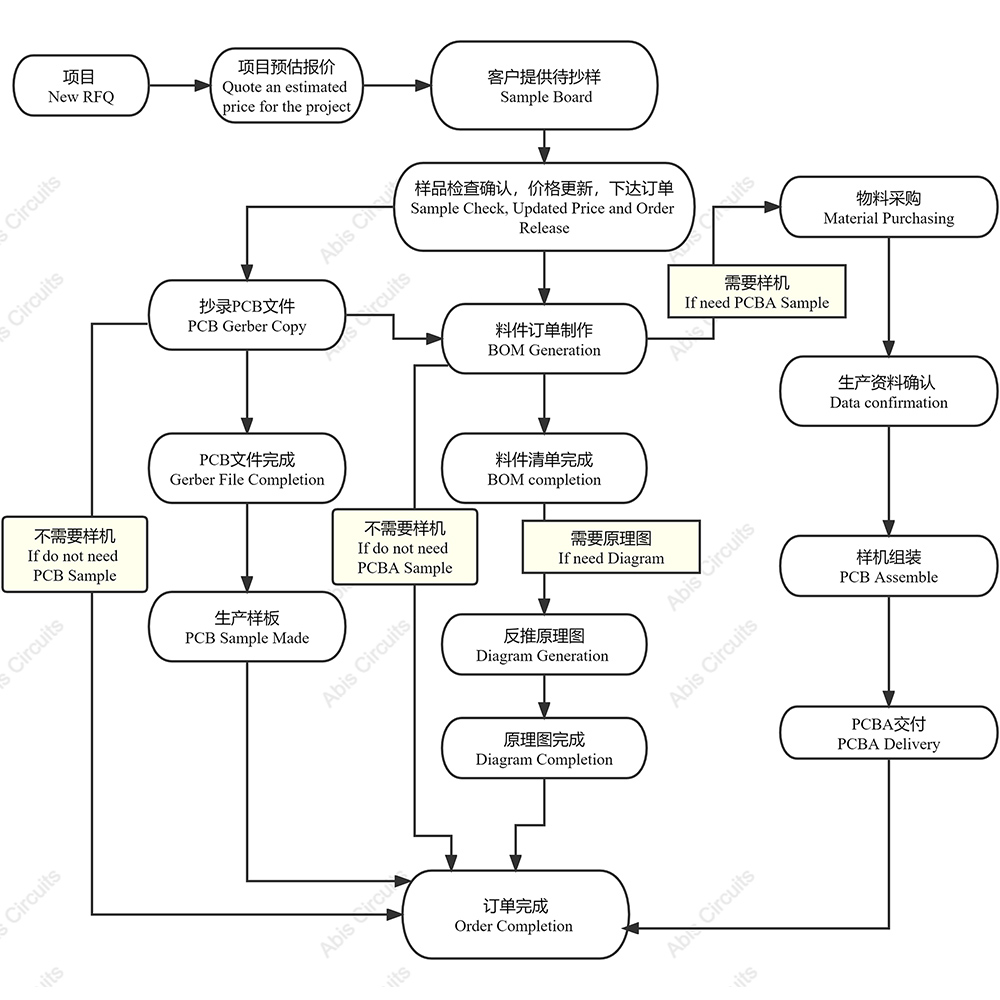

Nee, mir kënnen netakzeptéierenBilddateien, wann Dir keng huttGerberDatei, kënnt Dir eis Probe schécken fir se ze kopéieren.

PCB & PCBA Kopie Prozess:

Op Zäit Liwwerung Taux ass méi wéi 95%

a), 24 Stonnen séier Tour fir duebel Säit Prototyp PCB

b), 48 Stonnen fir 4-8 Schichten Prototyp PCB

c), 1 Stonn fir Zitat

d), 2 Stonnen fir Ingenieursfro / Feedback Feedback

e), 7-24 Stonnen fir technesch Ënnerstëtzung / Bestellungsservice / Fabrikatiounsoperatiounen

ABIS huet keng MOQ Ufuerderunge fir entweder PCB oder PCBA.

Mir bedeelegen all Joer un Ausstellungen, déi lescht sinn déiExpo Electronica& ElectronTechExpo a Russland vum Abrëll 2023. Freet Iech op Äre Besuch.

ABlS mécht 100% visuell an AOl Inspektioun wéi och elektresch Testen, Héichspannungstesten, Impedanzkontrolltesten, Mikro-Sektiounen, Thermalschocktesten, Löttesten, Zouverlässegkeetstesten, Isoléierresistenztesten, Ionesch Reinheetstester a PCBA Funktionell Testen.

a), 1 Stonn Zitat

b), 2 Stonnen Reklamatiounsfeedback

c), 7 * 24 Stonnen technesch Ënnerstëtzung

d), 7*24 Bestellungsservice

e), 7*24 Stonnen Liwwerung

f), 7*24 Produktiounslaf

| Produktiounskapazitéit vu waarme Verkafsprodukter | |

| Duebel Säit / Multilayer PCB Workshop | Aluminium PCB Workshop |

| Technesch Fäegkeet | Technesch Fäegkeet |

| Matière première: CEM-1, CEM-3, FR-4(High TG), Rogers, TELFON | Matière première: Aluminiumbasis, Kupferbasis |

| Layer: 1 Layer op 20 Layer | Layer: 1 Layer an 2 Layer |

| Min. Linn Breet / Raum: 3mil/3mil (0.075mm/0.075mm) | Min. Linn Breet / Raum: 4mil / 4mil (0.1mm / 0.1mm) |

| Min. Hole Gréisst: 0.1mm (Drilling Lach) | Min.Lach Gréisst: 12mil (0.3mm) |

| Max.Verwaltungsrot Gréisst: 1200mm * 600mm | Max Board Gréisst: 1200mm * 560mm (47in * 22in) |

| Fäerdeg Verwaltungsrot deck: 0.2mm-6.0mm | Fäerdeg Borddicke: 0,3 ~ 5mm |

| Kupferfolie Dicke: 18um ~ 280um (0.5oz ~ 8oz) | Kupferfolie Dicke: 35um ~ 210um (1oz ~ 6oz) |

| NPTH Lach Toleranz: +/-0,075 mm, PTH Lach Toleranz: +/-0,05 mm | Lach Positioun Toleranz: +/- 0,05 mm |

| Outline Toleranz: +/- 0,13 mm | Routing Kontur Toleranz: +/ 0,15 mm;Punching Outline Toleranz: +/ 0,1 mm |

| Fläch fäerdeg: Bleifräi HASL, Tauchgold (ENIG), Tauchsëlwer, OSP, Vergoldung, Goldfinger, Carbon INK. | Uewerfläch fäerdeg: Bleifräi HASL, Tauchgold (ENIG), Tauchsëlwer, OSP etc |

| Impedanz Kontroll Toleranz: +/- 10% | Bleiwen deck Toleranz: +/- 0,1 mm |

| Produktioun Muecht: 50.000 sqm / Mount | MC PCB Produktioun Muecht: 10.000 sqm / Mount |